# **GRAPHICAL SYMBOLS FOR DIAGRAMS -**

Part 12: Binary logic elements

### Chapter I: General

#### 1 Scope

This part of IEC 60617 contains graphical symbols that have been developed to represent logic functions. They are intended also to represent physical devices or combinations of physical devices capable of carrying out these functions. The symbols have been prepared with a view to electrical applications, but many can also be applied to non-electrical devices, for example pneumatic, hydraulic or mechanical.

#### 1A Normative references

The following normative documents contain provisions which, through reference in this text, constitute provisions of this part of IEC 60617. At the time of publication, the editions indicated were valid. All normative documents are subject to revision, and parties to agreements based on this part of IEC 60617 are encouraged to investigate the possibility of applying the most recent editions of the normative documents listed below. Members of IEC and ISO maintain registers of currently valid International Standards.

- IEC 60617-2: 1996, Graphical symbols for diagrams Part 2: Symbol elements, qualifying symbols and other symbols having general application

- IEC 60617-3: 1996, Graphical symbols for diagrams Part 3: Conductors and connecting devices

- IEC 60617-10: 1996, Graphical symbols for diagrams Part 10: Telecommunication: Transmission

- IEC 60617-13: 1993, Graphical symbols for diagrams Part 13: Analogue elements

- IEC 61082-1: 1991, Preparation of documents used in electrotechnology Part 1: General requirements

- IEC 61082-2: 1993, Preparation of documents used in electrotechnology Part 2: Functionoriented diagrams

- ISO 31-11: 1992, Quantities and units Part 11: Mathematical signs and symbols for use in the physical sciences and technology

#### 2 General notes

2.1 Symbols in accordance with the superseded IEC 60117-15: Recommended Graphical Symbols, Part 15: Binary Logic Elements, will be required for a prolonged changeover period but should be progressively superseded by the symbols given in this standard. Although non-preferred, the use of other symbols recognized by official national standards, that is distinctive shapes in place of symbols 12-27-01, 12-27-02, 12-27-09, 12-27-10, 12-27-11, 12-27-12, 12-28-01, 12-28-02 and 12-28-04, shall not be considered to be in contradiction with this standard. Usage of these other

- symbols in combination to form complex symbols (for example, use as embedded symbols) is discouraged.

- 2.2 For explanation of "logic states", "logic levels", etc., see IEC 61082-2.

- 2.3 This standard uses the symbols 0 and 1 to identify the two logic states of a binary variable. These states are referred to as 0-state and 1-state.

A binary variable may be equated to any physical quantity for which two distinct ranges can

- be defined. In this standard these distinct ranges are referred to as logic levels and are denoted H and L. H is used to denote the logic level with the more positive algebraic value, and L is used to denote the logic level with the less positive algebraic value.

2.5 In the case of a system in which logic states are equated with other qualities of a physical

- quantity (for example positive or negative pulses, presence or absence of a pulse), H and L may be used to represent these qualities or may be replaced by more suitable designations.

# 3 Explanation of terms

2.4

To facilitate understanding of the descriptions in the rest of this standard, it is useful to define three terms.

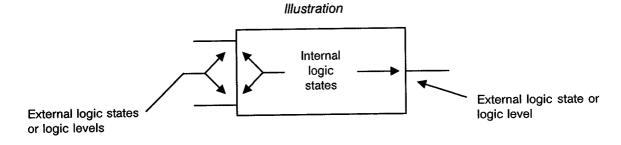

- 3.1 "Internal logic state" describes a logic state assumed to exist inside a symbol outline at an input or an output.

- 3.2 "External logic state" describes a logic state assumed to exist outside a symbol outline:

- on an input line prior to any external qualifying symbol at that input, or

- on an output line beyond any external qualifying symbol at that output.

- 3.3 "Logic level" describes the physical quality assumed to represent a logic state of a binary variable (see clauses 2.3 and 2.4).

### Chapter II: Symbol construction

#### Composition of the symbol

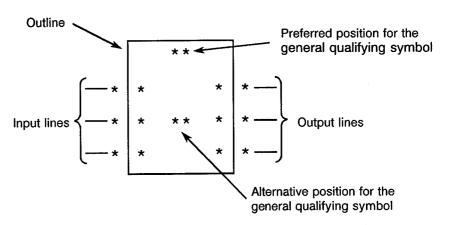

**4.1** A symbol comprises an outline or combination of outlines together with one or more qualifying symbols.

Application of the symbols requires in addition the representation of input and output lines.

The single asterisks (\*) denote possible positions for qualifying symbols relating to inputs and outputs.

If and only if the function of an element is completely determined by the qualifying symbols associated with its inputs and/ or outputs, no general qualifying symbol is needed.

- **4.2** General additional information may be included in a symbol outline as described in IEC 61082-1.

- **4.3** Information not standardized in this standard relating to a specific input [output] may be shown in square brackets inside the outline adjacent to the relevant input [output] and should follow [precede] any qualifying symbols applying to the input [output] as shown in symbol 12-28-14.

Additional information relating to the general logic function of the element may be shown in square brackets inside the outline.

- **4.4** All outputs of an element represented by a single unsubdivided symbol always have identical internal logic states determined by the function of the element except when indicated otherwise by an associated qualifying symbol or label inside the symbol outline. The subdivision of a symbol and the qualifying symbols referred to here include those explicitly shown and those only implied according to the simplification rules of clause 6.3.

- 4.5 In some figures, lowercase letters which are not part of the symbols have been shown outside the outline just to identify the inputs [outputs] as referred to in the description.

- **4.6** The symbols and descriptions in this standard are intended for signal flow from left to right. If a symbol is instead intended for right-to-left flow, this is explicitly stated in the description of the symbol or indicated in the symbol itself.

When interpreting a symbol, one should assume, unless otherwise indicated, that a terminal shown on the left with respect to the normal reading orientation of the labels inside the symbol is an input,

the left if it aids the layout of the diagram or better conveys the structure of the device.

The direction of signal flow shall be clearly implied or indicated. Explicit indication may be done by

and that one shown on the right is an output. Inputs may also be shown on the right and outputs on

using qualifying symbols that inherently indicate the direction of signal flow (such as qualifying symbols defined only for inputs or only for outputs, or general qualifying symbols that indicate flow direction) or by other symbols on the diagram that are connected to the terminal.

If the direction of signal flow on a terminal line is not otherwise obvious, that line shall be marked with an arrowhead (symbol 02-05-01 of IEC 60617-2) pointing in the direction of signal flow or with the symbol for bidirectional signal flow (symbol 12-10-02), whichever applies. No arrowhead shall touch the outline or any other qualifying symbol. See, for example, symbol 12-29-06.

4.7 The following symbols shall be oriented as described or shown within this standard with respect to the inputs, outputs and outlines of the elements in which they appear. That is, these symbols, together with any associated terminal lines, shall be mirrored when the direction of signal

flow is reversed:

10-15-01 Amplifier, general symbol (see IEC 60617-10)

12-07-01 Logic negation, shown at an input up to and including

including

12-08-06 Internal output (virtual output)

12-09-08A Output with special amplification

12-09-08B Input with special amplification

Internal connection

12-07-09

12-08-01 up to and

12-09-24

12-09-25

12-09-47

Dynamic input with polarity indicator

Bit grouping for multibit input

Bit grouping for multibit output

Line grouping at the input side

12-09-48 Line grouping at the output side

12-55-01 Bus indicator, unidirectional

See for example symbol 12 07 02 and its mirrored various 12 07 07

See, for example, symbol 12-07-03 and its mirrored version 12-07-05.

All other qualifying symbols shall be oriented as shown with respect to the text inside the element.

For more information about the orientation of symbols, see 4.3.4 of IEC 61082-1.